I am trying to interface my CFA533 (RS232) with my board which already have an FPGA.

But while starting, I got stuck using Wintest633 with my module. Can somebody help?

I am not quite sure about the CRC generating algorithm to be implemented in FPGA.

But while starting, I got stuck using Wintest633 with my module. Can somebody help?

I am not quite sure about the CRC generating algorithm to be implemented in FPGA.

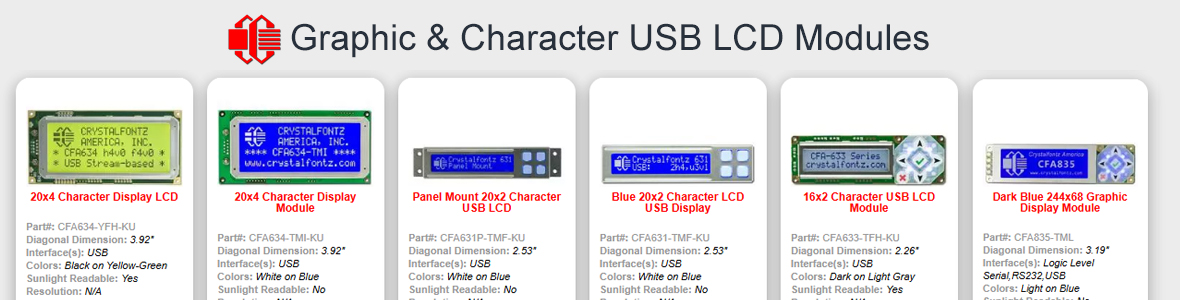

Looking for additional LCD resources? Check out our LCD blog for the latest developments in LCD technology.